### General Description

The MAX5069 is a high-frequency, current-mode, pulse-width modulation (PWM) controller (with dual MOSFET drivers) that integrates all the building blocks necessary for implementing AC-DC or DC-DC fixed-frequency power supplies. Isolated or nonisolated pushpull and half/full-bridge power supplies are easily constructed using either primary- or secondary-side regulation. Current-mode control with leading-edge blanking simplifies control-loop design and a programmable internal slope-compensation circuit stabilizes the current loop when operating at duty cycles above 50%.

An input undervoltage lockout (UVLO) programs the input-supply startup voltage and ensures proper operation during brownout conditions.

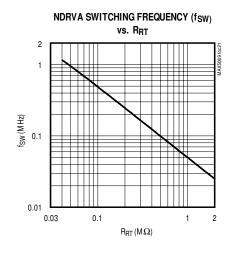

A single external resistor programs the oscillator frequency from 50kHz to 2.5MHz. The MAX5069A/D provide a SYNC input for synchronization to an external clock. The maximum FET-driver duty cycle for the MAX5069 is 50%. Programmable dead time allows additional flexibility in optimizing magnetic design and overcoming parasitic effects. Programmable hiccup current limit provides additional protection under severe faults.

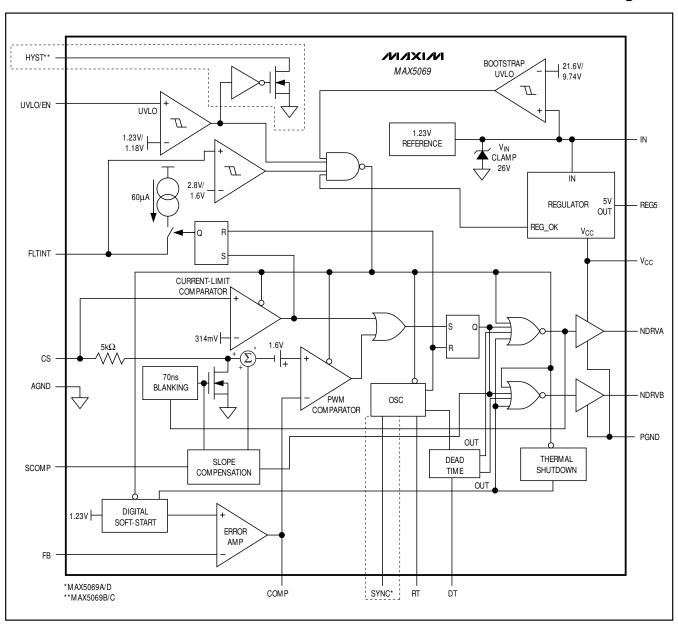

The MAX5069 is specified over the -40°C to +125°C automotive temperature range and is available in a 16-pin thermally enhanced TSSOP-EP package. Refer to the MAX5068 data sheet for single FET-driver applications.

Warning: The MAX5069 is designed to work with high voltages. Exercise caution.

### Applications

Universal-Input AC Power Supplies Isolated Telecom Power Supplies **Networking System Power Supplies** Server Power Supplies Industrial Power Conversion

### **Features**

- ♦ Current-Mode Control with 47µA (typ) Startup Current

- ♦ Oscillator Frequency Programmable to 2.5MHz

- Resistor-Programmable ±4.5% Accurate Switching Frequency

- **Dual Gate-Drive Output for Half/Full-Bridge or Push-Pull Applications**

- ♦ Rectified 85VAC to 265VAC, or 36VDC to 72VDC Input (MAX5069A/B)

- ♦ Input Directly Driven from 10.8V to 24V (MAX5069C/D)

- ♦ Programmable Dead Time and Slope Compensation

- Programmable Startup Voltage (UVLO)

- ♦ Programmable UVLO Hysteresis (MAX5069B/C)

- **♦** Frequency Synchronization Input (MAX5069A/D)

- ♦ -40°C to +125°C Automotive Temperature Range

- ♦ 16-Pin Thermally Enhanced TSSOP-EP Package

### Ordering Information

| PART        | TEMP RANGE      | PIN-PACKAGE  |

|-------------|-----------------|--------------|

| MAX5069AAUE | -40°C to +125°C | 16 TSSOP-EP* |

| MAX5069BAUE | -40°C to +125°C | 16 TSSOP-EP* |

| MAX5069CAUE | -40°C to +125°C | 16 TSSOP-EP* |

| MAX5069DAUE | -40°C to +125°C | 16 TSSOP-EP* |

<sup>\*</sup>EP = Exposed pad.

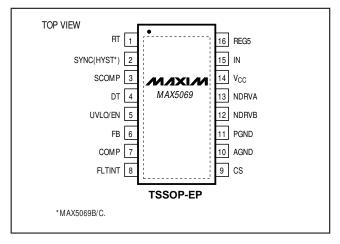

### Pin Configuration

Selector Guide appears at end of data sheet.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| IN to PGND                          | 0.3V to +30V                     | AGND to  |

|-------------------------------------|----------------------------------|----------|

| IN to AGND                          | 0.3V to +30V                     | Continuo |

| V <sub>CC</sub> to PGND             | 0.3V to +13V                     | 16-Pin   |

| VCC to AGND                         | 0.3V to +13V                     | Operatin |

| FB, COMP, CS, HYST, SYNC, REG5 to A | AGND0.3V to +6V                  | Maximur  |

| UVLO/EN, RT, DT, SCOMP, FLTINT to A | AGND0.3V to +6V                  | Storage  |

| NDRVA, NDRVB to PGND                | 0.3V to (V <sub>CC</sub> + 0.3V) | Lead Te  |

|                                     |                                  |          |

| AGND to PGND                                   | 0.3V to +0.3V  |

|------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70$ °C) |                |

| 16-Pin TSSOP-EP (derate 21.3mW/°C above        | +70°C)1702mW   |

| Operating Temperature Range                    | 40°C to +125°C |

| Maximum Junction Temperature                   | +150°C         |

| Storage Temperature Range                      | 60°C to +150°C |

| Lead Temperature (soldering, 10s)              | +300°C         |

|                                                |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN}=+12V \text{ for the MAX5069C/D},\ V_{IN}=+23.6V \text{ for the MAX5069A/B at startup, then reduces to } +12V,\ C_{IN}=C_{REG5}=0.1\mu\text{F},\ C_{VCC}=1\mu\text{F},\ R_{RT}=100\text{k}\Omega,\ NDRV_=\text{ floating},\ T_A=T_{MIN}\text{ to }T_{MAX},\ unless \text{ otherwise noted}.\ Typical values are at $T_A=+25^{\circ}C.$) (Note 1)$

| PARAMETER                                    | SYMBOL                                       | CONDITIONS                                                             |                          | MIN   | TYP   | MAX   | UNITS |  |  |

|----------------------------------------------|----------------------------------------------|------------------------------------------------------------------------|--------------------------|-------|-------|-------|-------|--|--|

| UNDERVOLTAGE LOCKOUT/ST                      | UNDERVOLTAGE LOCKOUT/STARTUP                 |                                                                        |                          |       |       |       |       |  |  |

| Bootstrap UVLO Wake-Up Level                 | V <sub>SUVR</sub>                            | V <sub>IN</sub> rising, MAX5069A/B                                     |                          | 19.68 | 21.6  | 23.60 | V     |  |  |

| Bootstrap UVLO Shutdown Level                | VsuvF                                        | V <sub>IN</sub> falling, MAX5069A                                      | /B                       | 9.05  | 9.74  | 10.43 | V     |  |  |

| UVLO/EN Wake-Up Threshold                    | V <sub>ULR2</sub>                            | UVLO/EN rising                                                         |                          | 1.205 | 1.230 | 1.255 | V     |  |  |

| UVLO/EN Shutdown Threshold                   | V <sub>ULF2</sub>                            | UVLO/EN falling                                                        |                          |       | 1.18  |       | V     |  |  |

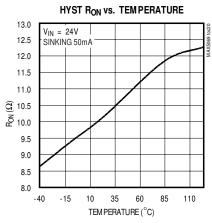

| HYST FET On-Resistance                       | R <sub>DS</sub> (ON)_H                       | MAX5069B/C only, sin VUVLO/EN = 0V                                     | king 50mA,               |       | 10    |       | Ω     |  |  |

| HYST FET Leakage Current                     | ILEAK_H                                      | VUVLO/EN = 2V, VHYST                                                   | = 5V                     |       | 3     |       | nA    |  |  |

| IN Supply Current In<br>Undervoltage Lockout | ISTART                                       | V <sub>IN</sub> = +19V, V <sub>UVLO/EN</sub>                           | < VULF2                  |       | 47    | 90    | μΑ    |  |  |

| IN Range                                     | V <sub>IN</sub>                              |                                                                        |                          | 10.8  |       | 24.0  | V     |  |  |

| INTERNAL SUPPLIES (VCC and                   | INTERNAL SUPPLIES (V <sub>CC</sub> and REG5) |                                                                        |                          |       |       |       |       |  |  |

| V <sub>CC</sub> Regulator Set Point          | VCCSP                                        | V <sub>IN</sub> = +10.8V to +24V, V <sub>CC</sub> sourcing 1µA to 25mA |                          | 7.0   |       | 10.5  | V     |  |  |

| REG5 Output Voltage                          | V <sub>REG5</sub>                            | I <sub>REG5</sub> = 0 to 1mA                                           |                          | 4.85  | 5.00  | 5.15  | V     |  |  |

| REG5 Short-Circuit Current Limit             | I <sub>REG5_SC</sub>                         |                                                                        |                          |       | 18    |       | mA    |  |  |

| IN Supply Current After Startup              | lu.                                          | V <sub>IN</sub> = +24V                                                 |                          | 7     |       | mA    |       |  |  |

| IN Supply Current After Startup              | I <sub>IN</sub>                              | VIN = +24V                                                             | f <sub>SW</sub> = 100kHz |       | 3     |       | ША    |  |  |

| Shutdown Supply Current                      | I <sub>VIN_SD</sub>                          |                                                                        |                          |       |       | 90    | μΑ    |  |  |

| GATE DRIVER (NDRVA, NDRVB)                   |                                              |                                                                        |                          |       |       |       |       |  |  |

| Driver Output Impedance                      | Z <sub>OUT(LOW)</sub>                        | NDRVA/NDRVB sinking 100mA                                              |                          |       | 2     | 4     | Ω     |  |  |

| Driver Output Impedance                      | Z <sub>OUT</sub> (HIGH)                      | NDRVA/NDRVB sourcing 25mA                                              |                          |       | 3     | 6     | 52    |  |  |

| Driver Peak Output Current                   | luppy (                                      | Sinking                                                                |                          |       | 1000  |       | mA    |  |  |

| Driver Feak Output Current                   | I <sub>NDRV</sub>                            | Sourcing                                                               |                          |       | 650   |       | IIIA  |  |  |

| PWM COMPARATOR                               |                                              |                                                                        |                          |       |       |       |       |  |  |

| Comparator Offset Voltage                    | Vos_pwm                                      | VCOMP > VCS                                                            |                          | 1.30  | 1.60  | 2.00  | V     |  |  |

| Comparator Propagation Delay                 | t <sub>PD_PWM</sub>                          | V <sub>CS</sub> = 0.1V                                                 |                          |       | 40    |       | ns    |  |  |

| Minimum On-Time                              | ton(MIN)                                     | Includes tcs_blank                                                     |                          |       | 110   |       | ns    |  |  |

| CURRENT-LIMIT COMPARATOR                     |                                              |                                                                        |                          |       |       |       |       |  |  |

| Current-Limit Trip Threshold                 | Vcs                                          |                                                                        |                          | 298   | 314   | 330   | mV    |  |  |

|                                              |                                              |                                                                        |                          |       |       |       |       |  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=+12V \text{ for the MAX5069C/D},\ V_{IN}=+23.6V \text{ for the MAX5069A/B at startup, then reduces to } +12V,\ C_{IN}=C_{REG5}=0.1\mu\text{F},\ C_{VCC}=1\mu\text{F},\ R_{RT}=100\text{k}\Omega,\ NDRV_=\text{ floating},\ T_A=T_{MIN}\ \text{to }T_{MAX},\ \text{unless otherwise noted}.\ Typical\ values\ \text{are at }T_A=+25^{\circ}\text{C.})\ (\text{Note 1})$

| PARAMETER                                        | SYMBOL               | CONDITIONS                                                     | MIN   | TYP   | MAX   | UNITS   |  |  |

|--------------------------------------------------|----------------------|----------------------------------------------------------------|-------|-------|-------|---------|--|--|

| CS Input Bias Current                            | I <sub>B_CL</sub>    | Vcs = 0V                                                       | 0     |       | +2    | μΑ      |  |  |

| CS Blanking Time                                 | tCS_BLANK            |                                                                |       | 70    |       | ns      |  |  |

| Propagation Delay from Comparator Input to NDRV_ | tPD_CL               | 50mV overdrive                                                 |       | 40    |       | ns      |  |  |

| IN CLAMP VOLTAGE                                 |                      |                                                                | •     |       |       |         |  |  |

| IN Clamp Voltage                                 | VIN_CLAMP            | IN sinking 2mA (Note 2)                                        | 24.0  | 26.0  | 29.0  | V       |  |  |

| ERROR AMPLIFIER (FB, COMP)                       |                      |                                                                |       |       |       |         |  |  |

| Voltage Gain                                     | A <sub>V</sub>       | $R_{COMP} = 100k\Omega$ to AGND                                |       | 80    |       | dB      |  |  |

| Unity-Gain Bandwidth                             | BW                   | $R_{COMP} = 100k\Omega$ to AGND,<br>$C_{LOAD} = 100pF$ to AGND |       | 5     |       | MHz     |  |  |

| Phase Margin                                     | PM                   | $R_{COMP} = 100k\Omega$ to AGND,<br>$C_{LOAD} = 100pF$ to AGND |       | 65    |       | Degrees |  |  |

| FB Input Offset Voltage                          | Vos_fb               |                                                                |       |       | 3     | mV      |  |  |

| COMP Clares Valtage                              | \/                   | High                                                           | 2.6   |       | 3.8   | V       |  |  |

| COMP Clamp Voltage                               | VCOMP                | Low                                                            | 0.4   |       | 1.1   | V       |  |  |

| Error-Amplifier Output Current                   | ICOMP                | Sinking or sourcing                                            | 0.5   |       |       | mA      |  |  |

| Defenses Velteres                                | V <sub>REF</sub>     | +25°C ≤ T <sub>A</sub> ≤ +125°C (Note 3)                       | 1.215 | 1.230 | 1.245 | - v     |  |  |

| Reference Voltage                                |                      | -40°C ≤ T <sub>A</sub> ≤ +125°C (Note 3)                       | 1.205 | 1.230 | 1.242 |         |  |  |

| Input Bias Current                               | I <sub>B_EA</sub>    |                                                                |       | 100   | 300   | nA      |  |  |

| COMP Short-Circuit Current                       | ICOMP_SC             |                                                                |       | 12    |       | mA      |  |  |

| THERMAL SHUTDOWN                                 |                      |                                                                |       |       |       |         |  |  |

| Thermal-Shutdown Temperature                     | T <sub>SD</sub>      |                                                                |       | +170  |       | °C      |  |  |

| Thermal Hysteresis                               | THYST                |                                                                |       | 25    |       | °C      |  |  |

| OSCILLATOR SYNC INPUT (MA                        | X5069A/D on          | y)                                                             |       |       |       |         |  |  |

| SYNC High-Level Voltage                          | V <sub>IH_SYNC</sub> |                                                                | 2.4   |       |       | V       |  |  |

| SYNC Low-Level Voltage                           | VIL_SYNC             |                                                                |       |       | 0.4   | V       |  |  |

| SYNC Input Bias Current                          | I <sub>B_SYNC</sub>  |                                                                |       | 10    |       | nA      |  |  |

| Maximum SYNC Frequency                           | fsync                | f <sub>OSC</sub> = 2.5MHz (Note 4)                             | 3.125 |       |       | MHz     |  |  |

| SYNC High-Level Pulse Width                      | tsync_hi             |                                                                | 30    |       |       | ns      |  |  |

| SYNC Low-Level Pulse Width                       | tsync_lo             |                                                                | 30    |       |       | ns      |  |  |

| DIGITAL SOFT-START                               |                      |                                                                |       |       |       |         |  |  |

| Soft-Start Duration                              | tss                  | (Note 5)                                                       |       | 2047  |       | Cycles  |  |  |

| Reference-Voltage Step                           | VSTEP                |                                                                |       | 9.7   |       | mV      |  |  |

| Reference-Voltage Steps During<br>Soft-Start     |                      |                                                                |       | 127   |       | Steps   |  |  |

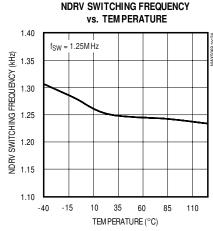

| OSCILLATOR                                       | •                    |                                                                | •     |       |       |         |  |  |

| Oscillator Frequency Range                       | fosc                 | $f_{OSC} = (10^{11} / R_{RT})$                                 | 50    |       | 2500  | kHz     |  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=+12V \text{ for the MAX5069C/D},\ V_{IN}=+23.6V \text{ for the MAX5069A/B} \text{ at startup, then reduces to } +12V,\ C_{IN}=C_{REG5}=0.1\mu\text{F},\ C_{VCC}=1\mu\text{F},\ R_{RT}=100\text{k}\Omega,\ NDRV_=\text{floating},\ T_A=T_{MIN}\ \text{to }T_{MAX},\ \text{unless otherwise noted}.\ Typical\ values\ \text{are at }T_A=+25^{\circ}\text{C.})\ (\text{Note 1})$

| PARAMETER                           | SYMBOL           | CONDITIONS                                           |                           | MIN                      | TYP  | MAX  | UNITS |

|-------------------------------------|------------------|------------------------------------------------------|---------------------------|--------------------------|------|------|-------|

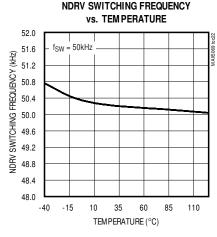

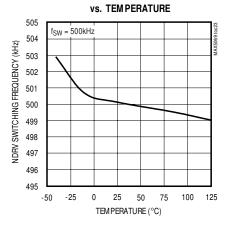

| NDRV_ Switching Frequency           | fsw              | $f_{SW} = 10^{11} / (2 \text{ x R}_{RT})$            |                           | 25                       |      | 1250 | kHz   |

| RT Voltage                          | V <sub>RT</sub>  | $40$ k $\Omega$ < R <sub>RT</sub> < $500$ k $\Omega$ |                           |                          | 2.0  |      | V     |

|                                     |                  | T 250C                                               | f <sub>OSC</sub> ≤ 500kHz | -2.5                     |      | +2.5 |       |

| Ossillator Assuracy                 |                  | $T_A = +25^{\circ}C$                                 | fosc > 500kHz             | -4                       |      | +4   | ]     |

| Oscillator Accuracy                 |                  | T 4000 / 40500                                       | fosc ≤ 500kHz             | -4.5                     |      | +4.5 | %     |

|                                     |                  | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       | fosc > 500kHz             | -6                       |      | +6   | 1     |

| Maximum Duty Cycle                  | D <sub>MAX</sub> | DT connected to REG5                                 |                           |                          | 100  |      | %     |

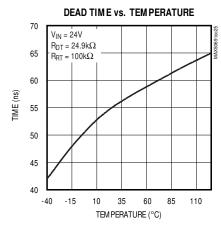

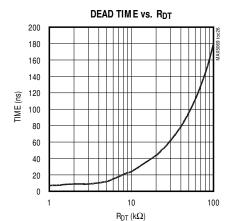

| DEAD-TIME CONTROL (DT)              |                  |                                                      |                           |                          |      |      |       |

| Dead Time                           | t <sub>DT</sub>  | $R_{DT} = 24.9k\Omega$                               |                           |                          | 60   |      | ns    |

| Dead-Time Disable Voltage           | VDT_DISABLE      |                                                      |                           | V <sub>REG5</sub> - 0.5V |      |      | V     |

| Dead-Time Regulation Voltage        | V <sub>DT</sub>  |                                                      |                           |                          | 1.23 |      | V     |

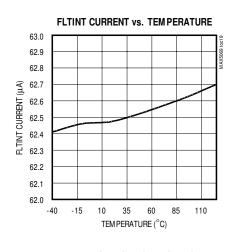

| INTEGRATING FAULT PROTECT           | TION (FLTINT)    |                                                      |                           |                          |      |      |       |

| FLTINT Source Current               | IFLTINT          | VFLTINT = 0V                                         |                           |                          | 60   |      | μΑ    |

| FLTINT Shutdown Threshold           | VFLTINT_SD       | V <sub>FLTINT</sub> rising                           |                           |                          | 2.8  |      | V     |

| FLTINT Restart Threshold            | VFLTINT_RS       | V <sub>FLTINT</sub> falling                          |                           |                          | 1.6  |      | V     |

| SLOPE COMPENSATION                  |                  |                                                      |                           |                          |      |      |       |

| Slope Compensation                  | VSLOPE           | C <sub>SLOPE</sub> = 100pf, RT = 1                   | 10kΩ                      |                          | 15   |      | mV/µs |

| Slope-Compensation Range            | VSLOPER          |                                                      |                           | 0                        |      | 90   | mV/μs |

| Slope-Compensation Voltage<br>Range | VSCOMP           |                                                      |                           | 0                        |      | 2.7  | V     |

- Note 1: The MAX5069 is 100% tested at  $T_A = +25^{\circ}C$ . All limits over temperature are guaranteed by design.

- Note 2: The MAX5069A/B are intended for use in universal-input power supplies. The internal clamp circuit is used to prevent the bootstrap capacitor (C1 in Figure 1) from charging to a voltage beyond the absolute maximum rating of the device when UVLO/EN is low. The maximum current to V<sub>IN</sub> (hence to clamp) when UVLO is low (device is in shutdown) must be externally limited to 2mA. Clamp currents higher than 2mA may result in clamp voltages higher than 30V, thus exceeding the absolute maximum rating for V<sub>IN</sub>. For the MAX5069C/D, do not exceed the 24V maximum operating voltage of the device.

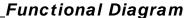

- Note 3: Reference voltage (V<sub>REF</sub>) is measured with FB connected to COMP (see the Functional Diagram).

- Note 4: The SYNC frequency must be at least 25% higher than the programmed oscillator frequency.

- Note 5: The internal oscillator clock cycle.

5

# High-Frequency, Current-Mode PWM Controller with Accurate Oscillator and Dual FET Drivers

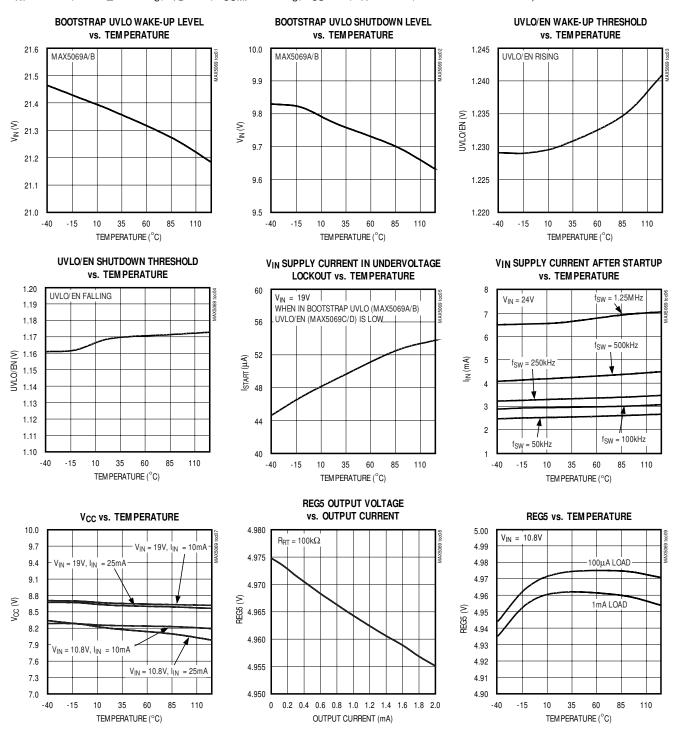

### Typical Operating Characteristics

$(V_{IN}=+23.6V \text{ for MAX5069A/B at startup}, \text{ then reduces to } +12V, V_{IN}=+12V \text{ for the MAX5069C/D}, C_{IN}=C_{REG5}=0.1 \mu F, C_{VCC}=1 \mu F, R_{RT}=100 k\Omega, NDRV_= \text{floating}, V_{FB}=0V, V_{COMP}=\text{floating}, V_{CS}=0V, T_A=+25^{\circ}C, \text{ unless otherwise noted.})$

Downloaded from: http://www.datasheetcatalog.com/

NIXIN

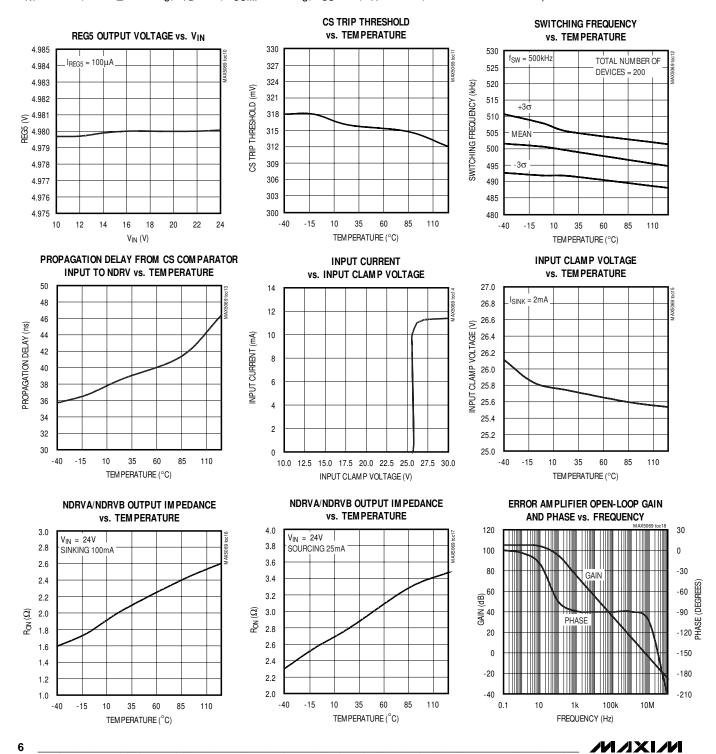

### Typical Operating Characteristics (continued)

$(V_{IN} = +23.6V \text{ for MAX5069A/B at startup}, \text{ then reduces to } +12V, V_{IN} = +12V \text{ for the MAX5069C/D}, C_{IN} = C_{REG5} = 0.1 \mu F, C_{VCC} = 1 \mu F, R_{RT} = 100 kΩ, NDRV_= \text{ floating}, V_{FB} = 0V, V_{COMP} = \text{ floating}, V_{CS} = 0V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

Downloaded from: http://www.datasheetcatalog.com/

### Typical Operating Characteristics (continued)

$(V_{IN} = +23.6V \text{ for MAX5069A/B at startup, then reduces to } +12V, V_{IN} = +12V \text{ for the MAX5069C/D, } C_{IN} = C_{REG5} = 0.1 \mu F, C_{VCC} = 1 \mu F, R_{RT} = 100 kΩ, NDRV_= \text{floating, } V_{FB} = 0V, V_{COMP} = \text{floating, } V_{CS} = 0V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

NDRV SWITCHING FREQUENCY

Pin Description

| PIN                  |                      |                 |                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------------------|----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX5069A<br>MAX5069D | MAX5069B<br>MAX5069C | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                            |  |  |

| 1                    | 1                    | RT              | Oscillator-Timing Resistor. Connect a resistor from RT to AGND to set the internal oscillator frequency.                                                                                                                                                                                                                            |  |  |

| 2                    | _                    | SYNC            | External-Clock Sync Input. Connect SYNC to AGND when not using an external clock.                                                                                                                                                                                                                                                   |  |  |

| _                    | 2                    | HYST            | Hysteresis Input                                                                                                                                                                                                                                                                                                                    |  |  |

| 3                    | 3                    | SCOMP           | Slope-Compensation Capacitor Connection                                                                                                                                                                                                                                                                                             |  |  |

| 4                    | 4                    | DT              | Dead-Time Resistor Connection. Connect a resistor from DT to AGND to program the output dead time. Connect to REG5 for NDRVA and NDRVB maximum 50% duty cycle.                                                                                                                                                                      |  |  |

| 5                    | 5                    | UVLO/EN         | Externally Programmable Undervoltage Lockout. UVLO/EN programs the input start voltage. Connect UVLO/EN to AGND to disable the output.                                                                                                                                                                                              |  |  |

| 6                    | 6                    | FB              | Error-Amplifier Inverting Input                                                                                                                                                                                                                                                                                                     |  |  |

| 7                    | 7                    | COMP            | Error-Amplifier Output                                                                                                                                                                                                                                                                                                              |  |  |

| 8                    | 8                    | FLTINT          | Fault-Integration Input. A capacitor connected to FLTINT charges with an internal 60µA current source during persistent current-limit faults. Switching terminates when V <sub>FLTINT</sub> is 2.8V. An external resistor connected in parallel discharges the capacitor. Switching resumes when V <sub>FLTINT</sub> drops to 1.6V. |  |  |

| 9                    | 9                    | CS              | Current-Sense Resistor Connection                                                                                                                                                                                                                                                                                                   |  |  |

| 10                   | 10                   | AGND            | Analog Ground. Connect to PGND.                                                                                                                                                                                                                                                                                                     |  |  |

| 11                   | 11                   | PGND            | Power Ground. Connect to AGND through a ground plane.                                                                                                                                                                                                                                                                               |  |  |

| 12                   | 12                   | NDRVB           | Gate-Driver Output B. Connect NDRVB to the gate of the external N-channel FET.                                                                                                                                                                                                                                                      |  |  |

| 13                   | 13                   | NDRVA           | Gate-Driver Output A. Connect NDRVA to the gate of the external N-channel FET.                                                                                                                                                                                                                                                      |  |  |

| 14                   | 14                   | V <sub>CC</sub> | 9V Linear-Regulator Output. Decouple V <sub>CC</sub> with a minimum 1μF ceramic capacitor to AGND; also internally connected to the FET drivers.                                                                                                                                                                                    |  |  |

| 15                   | 15                   | IN              | Power-Supply Input. IN provides power for all internal circuitry except the gate driver. Decouple IN with 0.1µF to AGND (see the <i>Typical Operating Circuit</i> ).                                                                                                                                                                |  |  |

| 16                   | 16                   | REG5            | 5V Linear-Regulator Output. Decouple REG5 to AGND with 0.1µF ceramic capacitor.                                                                                                                                                                                                                                                     |  |  |

| EP                   | EP                   | PAD             | Exposed Paddle. Connect to GND.                                                                                                                                                                                                                                                                                                     |  |  |

### Detailed Description

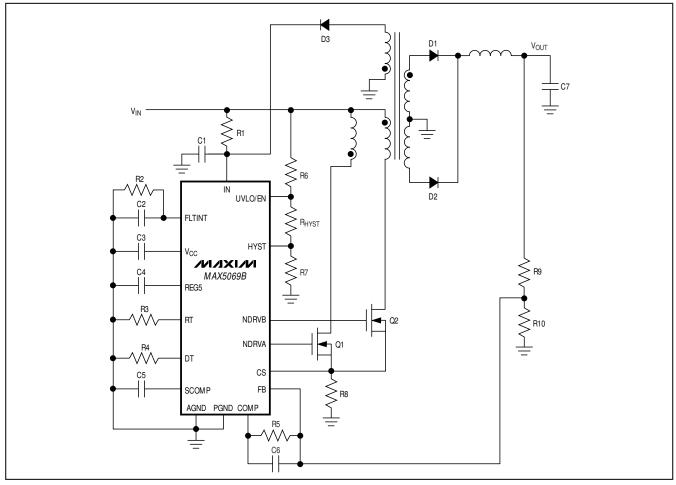

The MAX5069 is a current-mode, dual MOSFET driver, PWM controller designed for isolated and nonisolated push-pull or half-/full-bridge power-supply applications. A bootstrap UVLO with a programmable hysteresis, very low startup, and low operating current result in high-efficiency universal-input power supplies. In addition to the internal bootstrap UVLO, the device also offers programmable input startup and turn-off voltages, programmed through the UVLO/EN pin.

The MAX5069 includes a cycle-by-cycle current limit that turns off the gate drive to the external MOSFET during an overcurrent condition. The MAX5069 integrating fault protection reduces average power dissipation during persistent fault conditions (see the *Integrating Fault Protection* section).

The MAX5069 features a very accurate, wide-range, programmable oscillator that simplifies and optimizes the design of the magnetics. The MAX5069A/B are well suited for universal-input (rectified 85VAC to 265VAC) or telecom (-36VDC to -72VDC) power supplies. The MAX5069C/D are well suited for low-input voltage (10.8VDC to 24VDC) power supplies.

The MAX5069 high-frequency, universal input, offline/telecom, current-mode PWM controller integrates all the building blocks necessary for implementing AC-DC and DC-DC fixed-frequency power supplies. Pushpull and half-/full-bridge isolated or nonisolated power supplies are easily constructed using either primary- or secondary-side regulation. Current-mode control with leading-edge blanking simplifies control-loop design and the programmable slope compensation stabilizes the current loop when operating both FET drivers at a combined 100% duty cycle.

An input UVLO programs the input-supply startup voltage and ensures proper operation during brownout conditions. An external voltage-divider programs the supply startup voltage. The MAX5069B/C feature a programmable UVLO hysteresis. The MAX5069A/B feature an additional internal bootstrap UVLO with large hysteresis that requires a minimum startup voltage of 23.6V. The MAX5069A/D start up from a minimum voltage of 10.8V. Internal digital soft-start reduces output-voltage overshoot at startup.

A single external resistor programs the switching frequency of each MOSFET driver from 25kHz to 1.25MHz. The MAX5069A/D provide a SYNC input for synchronization to an external clock. The maximum FET

driver duty cycle for each driver is limited to 50%. Programmable dead time allows additional flexibility in optimizing magnetic design and overcoming parasitic effects. Integrating fault protection ignores transient overcurrent conditions for a set length of time. The length of time is programmed by an external capacitor. The internal thermal-shutdown circuit protects the device should the junction temperature exceed +170°C.

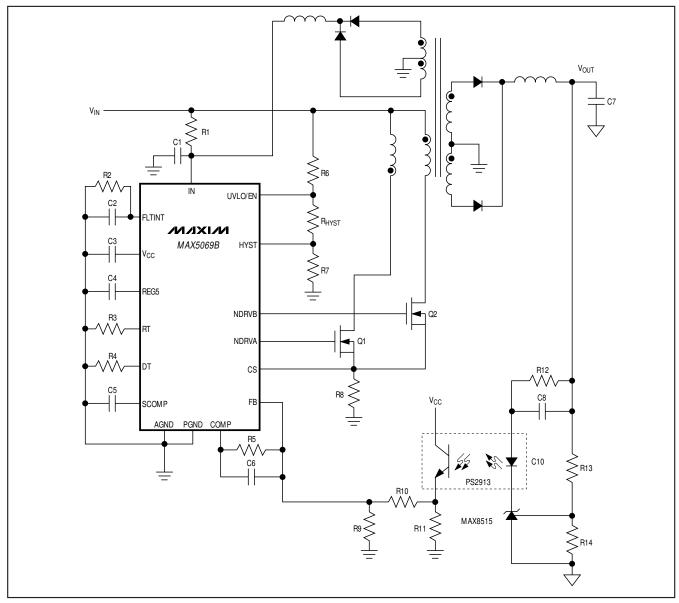

Power supplies designed with the MAX5069A/B use a high-value startup resistor, R1, which charges a reservoir capacitor, C1 (Figure 1). During this initial period, while the voltage is less than the internal bootstrap UVLO threshold, the device typically consumes only  $47\mu A$  of quiescent current. This low startup current and the large bootstrap UVLO hysteresis help to minimize the power dissipation across R1 even at the high end of the universal AC input voltage (265VAC).

The MAX5069 includes a cycle-by-cycle current limit that turns off the gates to both external MOSFETs during an overcurrent condition. When using the MAX5069A/B in the bootstrap mode (if the power-supply output is shorted), the tertiary winding voltage drops below the 9.74V threshold, causing the UVLO to turn off the gate to the external power MOSFETs. This reinitiates a startup sequence with soft-start.

### **Current-Mode Control**

The MAX5069 offers a current-mode control operation feature, such as leading-edge blanking with a dual internal path that only blanks the sensed current signal applied to the input of the PWM controller. The current-limit comparator monitors CS at all times and provides cycle-by-cycle current limit without being blanked. The leading-edge blanking of the CS signal prevents the PWM comparator from prematurely terminating the on cycle. The CS signal contains a leading-edge spike that results from the MOSFET's gate charge current, and the capacitive and diode reverse-recovery current of the power circuit. Since this leading-edge spike is normally lower than the current-limit comparator threshold, current limiting is provided under all conditions.

Use the MAX5069 in push-pull and half-/full-bridge applications where a large duty cycle is desired. The large duty cycle results in much lower operating primary RMS currents through the MOSFET switches, and in most cases it results in a smaller inductor and output filter capacitor. The MAX5069 adjusted slope compensation allows for easy stabilization of the inner current loop.

Figure 1. Nonisolated Power Supply with Programmable Input Supply Voltage

### **Undervoltage Lockout**

The MAX5069 features an input voltage UVLO/EN function to enable the PWM controller before any operation can begin. The MAX5069A/D shut down if the voltage at UVLO/EN falls below its 1.18V threshold. The MAX5069B/C also incorporate a UVLO hysteresis input to set the desired turn-off voltage.

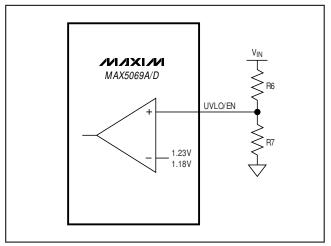

### MAX5069A/D UVLO Adjustment

The MAX5069A/D have an input voltage UVLO/EN with a 1.231V threshold. Before any operation can commence, the UVLO/EN voltage must exceed the 1.231V threshold. The UVLO circuit keeps the PWM comparator, ILIM comparator, oscillator, and output drivers shutdown to reduce current consumption (see the Functional Diagram).

Calculate R6 in Figure 2 by using the following formula:

$$R6 = \left(\frac{V_{ON}}{V_{ULR2}} - 1\right) \times R7$$

where  $V_{ULR2}$  is the UVLO/EN's 1.231V rising threshold and  $V_{ON}$  is the desired startup voltage. Choose an R7 value in the  $20 \mathrm{k}\Omega$  range.

After a successful startup, the MAX5069A/D shut down if the voltage at UVLO/EN drops below its 1.18V falling threshold.

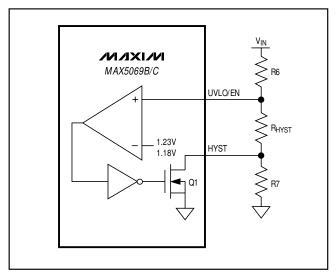

### MAX5069B/C UVLO with Programmable Hysteresis

In addition to programmable undervoltage lockout during startup, the MAX5069B/C incorporate a UVLO/EN

M/IXI/M

Figure 2. Setting the MAX5069A/D Undervoltage Lockout Threshold

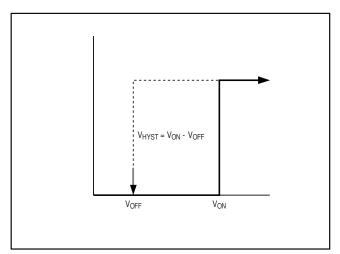

hysteresis that allows the user to set a voltage (VOFF) to disable the controller (see Figure 3).

At the beginning of the startup sequence, UVLO/EN is below the 1.23V threshold, and Q1 turns on connecting R<sub>HYST</sub> to GND (Figure 4). Once the UVLO 1.23V threshold is crossed, Q1 turns off, resulting in the series combination of R6, R<sub>HYST</sub>, and R7, placing the MAX5069 in normal operating condition.

Calculate the turn-on voltage ( $V_{\mbox{ON}}$ ) by using the following formula:

$$R6 = \left(\frac{V_{ON}}{V_{ULR2}} - 1\right) \times R_{HYST}$$

where  $V_{ULR2}$  is the UVLO/EN's 1.23V rising threshold.

Choose an RHYST value in the  $20k\Omega$  range.

The MAX5069 turns off when the MAX5069 UVLO/EN falls below the 1.18V falling threshold. The turn-off voltage (VOFF) is then defined as:

$$R7 = R6 / \left( \frac{V_{OFF}}{V_{ULF2}} - 1 \right) - R_{HYST}$$

where V<sub>ULF2</sub> is the 1.18V UVLO/EN falling threshold.

### Bootstrap Undervoltage Lockout (MAX5069A/B)

In addition to the externally programmable UVLO function offered by the MAX5069, the MAX5069A/B feature an additional internal bootstrap UVLO for use in high-voltage power supplies (see the *Functional Diagram*). This allows the device to bootstrap itself during initial

Figure 3. MAX5069 Hysteresis

Figure 4. Setting the MAX5069B/C Turn-On/Turn-Off Voltages

power-up. The MAX5069A/B start when  $V_{\mbox{\scriptsize IN}}$  exceeds the bootstrap UVLO threshold of 23.6V.

During startup, the UVLO circuit keeps the PWM comparator, ILIM comparator, oscillator, and output drivers shut down to reduce current consumption. Once V<sub>IN</sub> reaches 23.6V, the UVLO circuit turns on both the PWM and ILIM comparators, as well as the oscillator, and allows the output driver to switch. If V<sub>IN</sub> drops below 9.7V, the UVLO circuit shuts down the PWM comparator, ILIM comparator, oscillator, and output drivers, returning the MAX5069A/B to the startup mode.

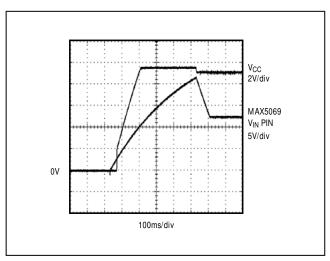

### MAX5069A/B Startup Operation

Normally, VIN is derived from the tertiary winding of the transformer. However, at startup there is no energy delivered through the transformer; hence, a special bootstrap sequence is required. Figure 5 shows the voltages on VIN and VCC during startup. Initially, both VIN and VCC are 0V. After the input voltage is applied, C1 charges through the startup resistor, R1, to an intermediate voltage (see Figure 1). At this point, the internal regulator begins charging C3 (see Figure 5). Only 47μA of the current supplied by R1 is used by the MAX5069A/B. The remaining input current charges C1 and C3. The charging of C3 stops when the VCC voltage reaches approximately 9.5V. The voltage across C1 continues rising until it reaches the wake-up level of 23.6V. Once VIN exceeds the bootstrap UVLO threshold, NDRVA/NDRVB begin switching the MOSFETs and energy is transferred to the secondary and tertiary outputs. If the voltage on the tertiary output builds to higher than 9.74V (the bootstrap UVLO lower threshold), startup ends and sustained operation commences.

If V<sub>IN</sub> drops below 9.74V before startup is complete, the device goes back to low-current UVLO. If this occurs, increase the value of C1 to store enough energy to allow for the voltage at the tertiary winding to build up.

### Startup Time Considerations for Power Supplies Using the MAX5069A/B

The V<sub>IN</sub> bypass capacitor, C1, supplies current immediately after wakeup (see Figure 1). The size of C1 and the connection configuration of the tertiary winding determine the number of cycles available for startup. Large values of C1 increase the startup time and also supply extra gate charge for more cycles during initial startup. If the value of C1 is too small, V<sub>IN</sub> drops below 9.74V because NDRVA/NDRVB do not have enough time to switch and build up sufficient voltage across the tertiary output that powers the device. The device goes back into UVLO and does not start. Use low-leakage capacitors for C1 and C3.

Generally, offline power supplies keep typical startup times to less than 500ms, even in low-line conditions (85VAC input for universal offline applications or 36VDC for telecom applications). Size the startup resistor, R1, to supply both the maximum startup bias of the device (90µA) and the charging current for C1 and C3. The bypass capacitor, C3, must charge to 9.5V, and C1 must charge to 24V, within the desired time period of 500ms. Because of the internal soft-start time of the MAX5069, C1 must store enough charge to deliver current to the device for at least 2047 oscillator clock cycles. To calculate the approximate amount of capacitance required, use the following formula:

Figure 5. VIN and VCC During Startup When Using the MAX5069 in Bootstrapped Mode (See Figure 1)

$$I_{g} = Q_{gtot} \times f_{SW}$$

$$C1 = \frac{(I_{IN} + I_{g}) \times t_{SS}}{V_{HYST}}$$

where I<sub>IN</sub> is the MAX5069's internal supply current after startup (3.3mA, typ),  $Q_{gtot}$  is the total gate charge for Q1 and Q2, fsw is the MAX5069's programmed output switching frequency,  $V_{HYST}$  is the bootstrap UVLO hysteresis (12V), and  $t_{SS}$  is the internal soft-start time (2047 clock cycles  $\times$  1 / fosc).

$$\begin{array}{ll} \text{Example:} & I_g = (16 nC) \; (250 \text{kHz}) \cong 4 \text{mA} \\ & f_{OSC} = 500 \text{kHz} \\ & t_{SS} = 2047 \; \text{x} \; (1 \; / \; f_{OSC}) = 4.1 \text{ms} \\ \\ \text{C1} & = \frac{(3.3 \text{mA} \; + \; 4 \text{mA}) \; (4.1 \text{ms})}{12 \text{V}} \; = \; 2.5 \mu \text{F} \end{array}$$

Use a 4.7µF ceramic capacitor for C1.

Assuming C1 > C3, calculate the value of R1 as follows:

$$\begin{split} I_{C1} &\cong \frac{V_{SUVR} \times C1}{500 ms} \\ R1 &\cong \frac{V_{IN(MIN)} - 0.5 \text{ x } V_{SUVR}}{I_{C1} + I_{START}} \end{split}$$

where V<sub>SUVR</sub> is the bootstrap UVLO wakeup level (23.6V max), V<sub>IN(MIN)</sub> is the minimum input supply voltage for the application (36V for telecom), and I<sub>START</sub> is the V<sub>IN</sub> supply current at startup (90µA, max).

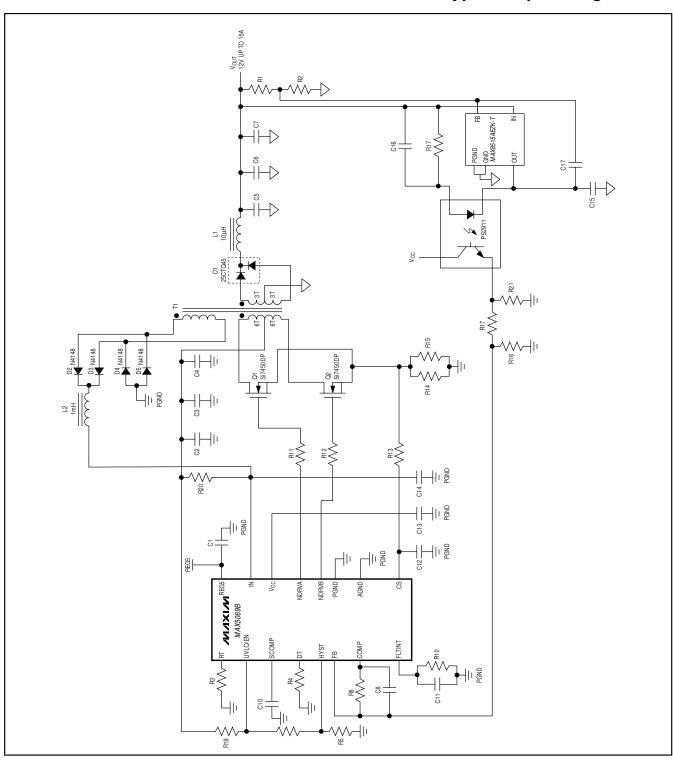

Figure 6. Secondary-Side, Regulated, Isolated Power Supply

For example:

$$\begin{split} I_{C1} &= \frac{24 V \ x \ 4.7 \mu F}{500 ms} = 225 \mu A \\ R1 &\cong \frac{36 V - 12 V}{225 \mu A + 90 \mu A} = 76 k \Omega \end{split}$$

To minimize power loss on this resistor, choose a higher value for R1 than the one calculated above (if a longer startup time can be tolerated).

The above startup method applies to a circuit similar to the one shown in Figure 1. In this circuit, the tertiary winding has the same phase as the secondary windings. Thus, the voltage on the tertiary winding at any given time is proportional to the output voltage. The minimum discharge time of C1 from 22V to 10V must be greater than the soft-start time (tss).

### Oscillator/Switching Frequency

Use an external resistor at RT to program the MAX5069 internal oscillator frequency from 50kHz to 2.5MHz. The MAX5069 NDRVA/NDRVB switching frequency is one half of the programmed oscillator frequency with a maximum 50% duty cycle.

Use the following formula to calculate the internal oscillator frequency:

$$f_{\rm osc} = \frac{10^{11}}{R_{\rm RT}}$$

where  $f_{OSC}$  is the oscillator frequency and  $R_{RT}$  is a resistor connected from RT to AGND.

Choose the appropriate resistor at RT to calculate the desired switching frequency (fsw):

$$R_{RT} = \frac{10^{11}}{2f_{SW}}$$

For the maximum 50% duty cycle at NDRVA/NDRVB, connect DT to REG5.

#### Dual N-Channel MOSFET Switch Driver

The MAX5069 drives two external N-channel MOSFETs in push-pull isolated power supplies. Each MOSFET driver operates with a maximum 50% duty cycle. The NDRV\_ outputs are supplied by the internal regulator (VCC), which is internally set to approximately 9.5V. For the universal input voltage range, the MOSFETs used must be able to withstand at least twice the DC level of the high-line input voltage. Both NDRVA and NDRVB can source and sink in excess of 650mA and 1000mA peak current, respectively.

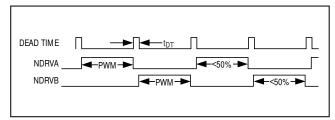

#### Dead-Time Control

In typical push-pull designs, it is desirable to add some extra delay between the turning off of one MOSFET and the turning on of the next MOSFET (Figure 7). The extra time ensures that the first MOSFET is fully off when the other MOSFET starts to turn on. This prevents both MOSFETs from being on simultaneously, thus avoiding

Figure 7. MAX5069 Dead-Time Timing Diagram

shorting out the transformer's primary. The MAX5069 allows the dead-time delay required to turn on the NDRVB FET after the NDRVA FET turns off. The dead time can be programmed to a minimum of 30ns to 1 / (0.5 x fsw). Connect a resistor between DT and AGND to set the desired dead time. Calculate the dead time using the following formula:

Dead time =

$$\frac{60}{29.4} \times R_{DT}(ns)$$

where  $R_{DT}$  is in  $k\Omega$  and the dead time is in ns.

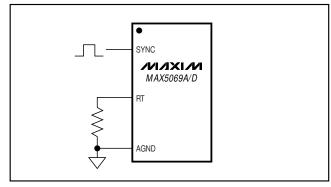

### External Synchronization (MAX5069A/D)

The MAX5069A/D can be synchronized using an external clock at the SYNC input. For proper frequency synchronization, the SYNC's input frequency must be at least 25% higher than the MAX5069A/D programmed internal oscillator frequency. Connect SYNC to AGND when not using an external clock.

### Integrating Fault Protection

The integrating fault-protection feature allows transient overcurrent conditions to be ignored for a programmable amount of time, giving the power supply time to behave like a current source to the load. For example, this can occur under load-current transients when the control loop requests maximum current to keep the output voltage from going out of regulation. Program the fault-integration time by connecting an external suitably sized capacitor to the FLTINT. Under sustained overcurrent faults, the voltage across this capacitor ramps up towards the FLTINT shutdown threshold (typically 2.8V). Once the threshold is reached, the power supply shuts down. A high-value bleed resistor connected in parallel with the FLTINT capacitor allows it to discharge towards the restart threshold (typically 1.6V). Once this threshold is reached, the supply restarts with a new soft-start cycle.

Figure 8. External Synchronization of the MAX5069A/D

Note that cycle-by-cycle current limiting is provided at all times by CS with a threshold of 314mV (typ). The fault-integration circuit forces a  $60\mu A$  current onto FLTINT each time that the current-limit comparator is tripped (see the *Functional Diagram*). Use the following formula to calculate the value of the capacitor necessary for the desired shutdown time of the circuit:

$$C_{FLTINT} \cong \frac{I_{FLTINT} \times t_{SH}}{2.8V}$$

where  $I_{FLTINT}=60\mu A$ ,  $t_{SH}$  is the desired fault-integration time during which current-limit events from the current-limit comparator are ignored. For example, a  $0.1\mu F$  capacitor gives a fault-integration time of 4.7ms.

This is an approximate formula. Some testing may be required to fine-tune the actual value of the capacitor. To calculate the recovery time, use the following formula:

$$R_{FLTINT} \; \cong \; \frac{t_{RT}}{0.595 \, \times \, C_{FLTINT}}$$

where t<sub>RT</sub> is the desired recovery time.

Choose  $t_{RT} = 10 \times t_{SH}$ . Typical values for  $t_{SH}$  range from a few hundred microseconds to a few milliseconds.

#### Soft-Start

The MAX5069 soft-start feature allows the load voltage to ramp up in a controlled manner, eliminating output-voltage overshoot. Soft-start begins after UVLO is deasserted. The voltage applied to the noninverting node of the amplifier ramps from 0 to 1.23V in 2047 oscillator clock cycles (soft-start timeout period). Unlike other devices, the MAX5069 reference voltage to the internal amplifier is soft-started. This method results in superior control of the output voltage under heavy- and light-load conditions.

### Internal Regulators

Two internal linear regulators power the MAX5069 internal and external control circuits. VCC powers the external N-channel MOSFETs and is internally set to approximately 9.5V. The REG5 5V regulator has a 1mA sourcing capability and may be used to provide power to external circuitry. Bypass VCC and REG5 with 1µF and 0.1µF high quality capacitors, respectively. Use lower value ceramics in parallel to bypass other unwanted noise signals. Bootstrapped operation requires startup through a bleed resistor. Do not excessively load the regulators while the MAX5069 is in the power-up mode. Overloading the outputs may cause the MAX5069 to fail upon startup.

### Error Amplifier

The MAX5069 includes an internal error amplifier that can regulate the output voltage in the case of a nonisolated power supply (Figure 1). Calculate the output voltage using the following equation:

$$V_{OUT} = \left(1 + \frac{R9}{R10}\right) x V_{REF}$$

where V<sub>REF</sub> = 1.23V. The amplifier's noninverting input internally connects to a digital soft-start reference voltage. This forces the output voltage to come up in an orderly and well-defined manner under all load conditions.

### Slope Compensation

The MAX5069 uses an internal-ramp generator for slope compensation. The internal-ramp signal resets at the beginning of each cycle and slews at the rate programmed by the external capacitor connected at SCOMP and the resistor at RT. Adjust the MAX5069 slew rate up to 90mV/µs using the following equation:

$$SR = \frac{165 \times 10^{-6}}{R_{RT} \times C_{SCOMP}} (mV/\mu s)$$

where R<sub>RT</sub> is the external resistor at RT that sets the oscillator frequency and C<sub>SCOMP</sub> is the capacitor at SCOMP.

### PWM Comparator

The PWM comparator uses the instantaneous current, the error amplifier, and the slope compensation to determine when to switch NDRVA and NDRVB off. In normal operation, the N-channel MOSFETs turns off when:

where Iprimary is the current through the N-channel MOSFETs, VEA is the output voltage of the internal amplifier, VOFFSET is the 1.6V internal DC offset, and VSCOMP is the ramp function starting at zero and slewing at the programmed slew rate (SR). When using the MAX5069 in a forward-converter configuration, the following conditions must be met to avoid current-loop subharmonic oscillations:

$$\frac{N_S}{N_P} \times \frac{K \times R_{CS} \times V_{OUT}}{L} = SR$$

where K = 0.75 and N<sub>S</sub> and N<sub>P</sub> are the number of turns on the secondary and primary side of the transformer, respectively. L is the secondary filter inductor. When optimally compensated, the current loop responds to input-voltage transients within one cycle.

### **Current Limit**

The current-sense resistor (RCS), connected between the source of the MOSFET and ground, sets the current limit. The CS input has a voltage trip level (VcS) of 314mV. Use the following equation to calculate the value of Rcs:

$$R_{CS} = \frac{V_{CS}}{I_{PRI}}$$

where IPRI is the peak current in the primary that flows through the MOSFET at full load.

When the voltage produced by this current (through the current-sense resistor) exceeds the current-limit comparator threshold, the MOSFET drivers (NDRVA/NDRVB) quickly terminate the current on-cycle. In most cases, a small RC filter is required to filter out the leading-edge spike on the sense waveform. Set the corner frequency to a few MHz above the switching frequency.

### \_Applications Information

### Layout Recommendations

Keep all PC board traces carrying switching currents as short as possible, and minimize current loops.

For universal AC input design, follow all applicable safety regulations. Offline power supplies may require UL, VDE, and other similar agency approvals. Contact these agencies for the latest layout and component rules.

Typically, there are two sources of noise emission in a switching power supply: high di/dt loops and high dV/dt surfaces. For example, traces that carry the drain current often form high di/dt loops. Similarly, the heatsink of the MOSFET presents a dV/dt source, thus minimize the surface area of the heatsink as much as possible.

To achieve best performance and to avoid ground loops, use a solid ground-plane connection.

### Selector Guide

| PART     | BOOTSTRAP<br>UVLO | STARTUP<br>VOLTAGE (V) | PROGRAMMABLE<br>UVLO<br>HYSTERESIS | OSCILLATOR SYNC |

|----------|-------------------|------------------------|------------------------------------|-----------------|

| MAX5069A | Yes               | 23.6                   | No                                 | Yes             |

| MAX5069B | Yes               | 23.6                   | Yes                                | No              |

| MAX5069C | No                | 10.8                   | Yes                                | No              |

| MAX5069D | No                | 10.8                   | No                                 | Yes             |

Typical Operating Circuit

MIXIM

Chip Information

TRANSISTOR COUNT: 4266 PROCESS: BICMOS

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_\_\_